FPGAプロジェクト生成自動化とソースコード管理(Vivado編)

概要

Vivadoを用いたFPGAのコード管理に関して記載します。 ソースコード(HDL、IP、BlockDesign,制約)を並べてバッチファイル(Windows)で自動生成する仕組みについて紹介します。 管理するファイルがソース関連だけになり、ある程度大規模なFPGAにおいても多くても数MByteです。 GITと連携しソースコード管理と複数人でのFPGA開発を容易にします。

※ArtixのMicroBlazeDesignのデモ(vivado2018.1)を紹介します。 github.com

背景

Vivadoを用いてFPGAをつくるときプロジェクトベースで管理すると容量が大きいファイルがたくさんできる。

たぶんIPの生成データとか中間データとか配置配線データとか含んでいる。

色々な日時のデータ(大規模だと1個1GByte超える)を保管しているとすぐにPCがパンクして困ってしまう。

FPGAのプロジェクトごと管理するのでなく、ソースコードだけ管理する仕組みを作りたい。

この辺はベンダーもたしか推奨していた手法な気がする。(うろ覚えですみません)

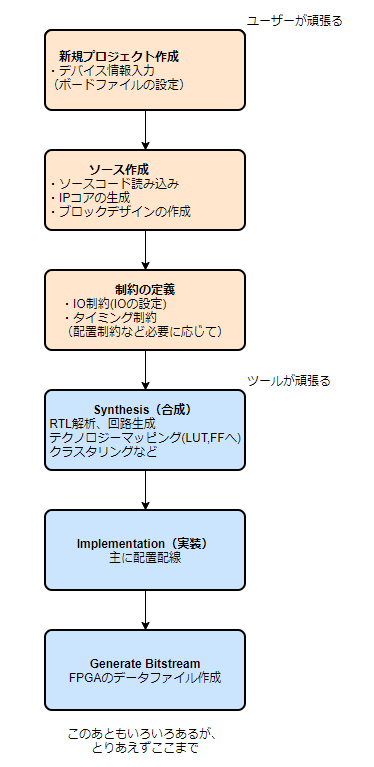

FPGAの作成フロー(ざっくり)

FPGAのプロジェクトフローを何となく書きます。

これを最初はGUIで作ると思います。(最初からコマンドモードで実施するすごい人もいるかもしれません。)

VivadoのGUIで作って、Bitstreamができて「おーよかったよかった」となるのですが、そのプロジェクトセット全体を今後も保管(管理?)し続けるのは大変です。

結局GUIをいじった挙句、必要になるのはおおよそ以下のファイルです。

・HDL(VHDL,Verilog)

・IPコアファイル (.xci)

・ブロックデザイン生成ファイル(.tcl)

・制約ファイル(.xdc)

このファイルだけを管理して、FPGA生成はバッチとTCLコマンドで自動化できるとプロジェクトファイルが軽くなります。

(もちろんリリースごとでは配置配線データを含むプロジェクトを残しておくと思います。)

デモのフォルダ構成

紹介するデモのフォルダ構成は大体こんな感じです。

・src ・・・HDL,Blockデザイン生成ファイル、IPファイル

・tcl ・・・制約ファイル

・xdc ・・・制約ファイル

・ReadMe.md

・build.bat

batを実行すると

・build フォルダが生成され

その下に日時フォルダ「 20200712-1253(西暦,月,日,-,時,分)」ができ、その下でツールが作業を始めます。

自動化の紹介

では一連の流れを自動化してみます。

Batファイルの起動からひとつひとつ記載いたします。(今回はWindowsですが、Linuxではシェルになると思います。)

(1)Vivado起動(非プロジェクトモード)

Build.batは以下の処理を行います。

(記事記載時点ではcompile.batとなってます。コンパイルとは意味が違うためBuild.batに修正予定。)

・Buildフォルダを作る。(Build日時と時間をファルダ名とする。)

2020年7月8日21時55分の場合は 20200708_2155というフォルダがbuildに生成される。

・Vivadoを非プロジェクトモードで起動

do_build.tclを与えて次にやることはこの中に入れております。

build.bat

@echo off set dt=%date% set tm=%time: =0% set FName=%dt:~-10,4%%dt:~-5,2%%dt:~-2,2%_%tm:~-11,2%%tm:~-8,2% mkdir build cd build mkdir %FName% cd %FName% xcopy ..\..\tcl tcl /D /S /R /Y /I /K C:\Xilinx\Vivado\2018.1\bin\vivado.bat -mode tcl -source tcl/do_build.tcl

(2)プロジェクト生成とソースインポート

do_build.tclの中は以下の通り。

build.bat

source tcl/import_project.tcl source tcl/run.tcl

import_project.tcl はだいたいフロー図のオレンジの部分です。 run.tcl はだいたいフロー図のブルーの部分です。

ではimport_projec.tclを見ていきます。

# Create project create_project arty_mb arty_mb -part xc7a35ticsg324-1L set_property board_part digilentinc.com:arty:part0:1.1 [current_project] # import source file source "../../src/mb/bd/arty_mb.tcl" add_files ../../src/mb/wrapper/arty_mb_wrapper.v add_files ../../src/top/arty_mb_top.v # import Ip core # import library # import constrs import_files -force #import_files -fileset constrs_1 -force -norecurse ../../xdc/system.xdc import_files -fileset constrs_1 -force -norecurse ../../xdc/arty_io.xdc import_files -fileset constrs_1 -force -norecurse ../../xdc/arty_timing.xdc

最初にデバイス名を指定してプロジェクトを作ります。

今回はArtyという評価ボード用プロジェクトのため、ボードのファイルを指定しています。

次にMicroBlazeとUARTコアを含んだブロックデザインを生成するtclを読み込みます。

これはGUIで作成した後、ExportBlockDesignで生成できます。本TCLを管理すればBlockデザインの差分を追えます。

(BlockDesignのレイアウトを管理することも可能ですが、今回は触れません。)

(3)合成と実装

次にrun.tclを見てみます。

SynthesisとImplementation,Bitstream生成とレポートの生成を行います。

# Mimic GUI behavior of automatically setting top and file compile order update_compile_order -fileset sources_1 update_compile_order -fileset sim_1 # Launch Synthesis launch_runs synth_1 wait_on_run synth_1 open_run synth_1 -name netlist_1 # Generate a timing and power reports and write to disk report_timing_summary -delay_type max -report_unconstrained -check_timing_verbose -max_paths 10 -input_pins -file ./syn_timing.rpt report_power -file ./syn_power.rpt # Launch Implementation launch_runs impl_1 -to_step write_bitstream wait_on_run impl_1 # Generate a timing and power reports and write to disk # comment out the open_run for batch mode open_run impl_1 report_timing_summary -delay_type min_max -report_unconstrained -check_timing_verbose -max_paths 10 -input_pins -file ./imp_timing.rpt report_power -file ./imp_power.rpt # comment out the for batch mode # start_gui # end exit

以上でFPGA生成の自動化ができました。

このソースコードと生成コマンド一式をGITで管理すればめでたくFPGAのコード管理ができるようになります。

本環境に関して

本環境はGitHubにあげております。

github.com

<環境>

・Vivado2018.1

・Vivadoが以下の場所にインストールされている。異なる場合はBatの該当部分を変えてください。

C:\Xilinx\Vivado\2018.1

・ArtyのBSPが入っていること。(※1に導入方法を記載。)

注釈

※1 Arty Board fileに関して

以下にArtyのBoardファイルがあります。

https://reference.digilentinc.com/reference/software/vivado/board-files?redirect=1

ダウンロードしてファイルを解凍します。

生成されたartyフォルダをVivadoインストールファルダのdata\boards\board_files に格納します。

最後に

ここまで読んでくださった方がおりましたらありがとうございます。

なかなかこの辺の手順に関しては情報があったりなかったりという気がします。

ISEツールでも同様の手順にてGITとの連携が可能ですが、環境構築していく上での情報がもっと少なく感じました...